シリコンフォトニクス技術による先進的高性能コンピューティングの促進

李佩雯 教授研究チーム

國立陽明交通大學 電子研究所

-

|

1. シリコンフォトニクス技術で従来型の高速コンピューティングを強化(classical high performance, energy-efficiency computing) |

世界中のデータセンターや現在普及している人工知能アプリケーション製品(ChatGPT、DeepSeekなど)は、膨大な量のデータを処理および計算するために、高効率でエネルギー効率の高いハードウェア(プロセッサチップや回路システムを含む)を早急に必要としています。しかし、CPUやGPUなどの商用コアプロセッサの性能(つまり、単位エネルギーあたりに実行できる演算数(computations per Joule))は、2010年代半ばにはすでに飽和状態に達しており、それ以降は大きな進歩がありません。これは、長年続いたムーアの法則が限界に達し、トランジスタサイズや技術ノードの単純な縮小だけでは、演算効率とエネルギー消費のバランスをとることが難しくなったためです。短チャネル効果により、トランジスタのリーク電流(エネルギー消費)は急激に増加します。さらに、電子部品の実装密度を高めるために、金属線の直径を可能な限り小さくして超長距離金属配線(electrical interconnect)による電気的相互接続を実現していますが、これはエネルギー消費と速度遅延を引き起こす大きな技術的ボトルネックとなっています。マルチコアプロセッサを使用することでコンピューティングシステム全体のパフォーマンスが向上しますが、プロセッサシステム内のボード間(board-to-board)やチップ間(chip-to-chip)の接続には依然としてケーブルや金属配線で接続されています。マルチコアプロセッサの数が増えるほど、インターフェースで使用される電気的接続の頻度と複雑性が増加し、コンピューティングシステム全体のパフォーマンスが大幅に低下します。

近年、シリコンフォトニクス技術は、効率的で省エネなコンピューティングシステムを推進するための最良の推進力(booster)となっています。光信号の持つ、エネルギー消費ゼロでの高速伝送という理想的な特性を活かし、「光インターコネクト(optical interconnect)」を「電気インターコネクト」の補助や代替として利用できれば、電荷信号伝送における遅延やエネルギー消費のジレンマを打破、改善できるはずです。データセンターではすでに、回路基板間のインターフェースにおけるケーブル接続を置き換えるために、第1世代のシリコンフォトニクス技術が使用されています。いわゆるプラガブル(pluggable)な光トランシーバーモジュールを使用し、光信号を光ファイバーを介して送信した後、電気信号に変換して金属配線を通じてスイッチに送ります。光ファイバーと金属配線が共存するこの伝送路は、使用するケーブルの量や長さを効果的に削減しますが、金属線によって発生する「熱」と電気信号強度の減衰という問題が依然として残ります。そこで、NVIDIA、AMD、Qualcommなどのチップ設計企業は、半導体製造企業(Intel、TSMC、Samsung、GlobalFoundriesなど)に対して、第2世代または2.5世代のコパッケージドオプティクス(Co-packaged optics, CPO)を提案しています。つまり、元々プリント基板(PCB)全体に分散していた光電子モジュール(光受信機、光導波路、光変調器、電流・電圧増幅器、ドライバIC、スイッチなど)を、単一のシリコンチップ上に統合することで、配線の使用を大幅に削減し、計算速度、帯域幅の向上、消費電力の削減という効果が期待されています。

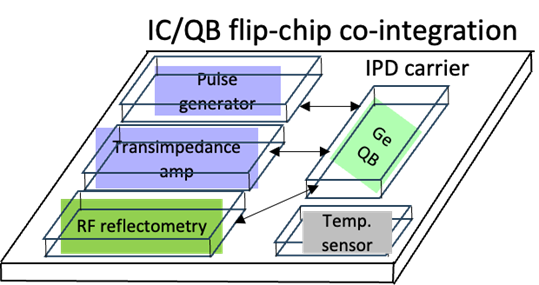

TSMCは、2024年12月にサンフランシスコで開催されたIEDM国際会議において、データセンター向けの新しい先進的なシリコンフォトニクスおよびパッケージング技術「COmpact Universal Photonic Engine(COUPE)」を発表しました[1–4]。個々の光学部品(ゲルマニウム光検出器、マイクロリング光変調器、窒化シリコン/シリコン光導波路、外部光ファイバーに接続するためのグレーティングカプラ(Grating Coupler)とエッジカプラ(Edge Coupler)、温度センサーなど)のプロセス設計キット(process design kit, PDK)を用意し、チップ設計企業向けに提供しています。TSMCはシリコンフォトニクスエンジンに関する複数の論文を発表し、CoWoS(Chip-on-Wafer-on-Substrate)パッケージング技術を用いた電子集積回路(IC)チップとシリコンフォトニクス回路チップの統合を実証しました。TSMCは、2025年にPCB上にコパッケージされたプラガブル(pluggable)光トランシーバーモジュールを正式にリリースし、2026年には基板(substrate)上の光ICと電子ICの平面(planar)集積、およびインターポーザー(interposer)上の光ICと電子ICの垂直積層統合(vertically-stacking)技術を発表する予定です。

多くの先進的な電子プロセッサやICシステムは、高度で堅牢なCMOSプロセス技術を用いて製造されていますが、垂直方向にスタック可能なシリコンフォトニック-電子ICをシリコンプラットフォーム上で実現することは容易ではありません。まず、光ICの光学部品(半導体レーザー、光検出器、光変調器、特に光導波路など)の幾何学的寸法(例えば、透過光の波長に応じたサブミクロン(sub-μm)またはミクロン(μm)レベルの特徴的な長さまたは膜厚、これは主に透過光の波長に依存します)は、電子ICの電子部品(トランジスタ、コンデンサなど)の幾何学的寸法よりもはるかに大きなものになります。さらに、光学素子間の接続は光結合(coupling)に重点を置いています。光結合損失(coupling loss)を低減するためには、結合面積または結合長さを通常、平方ミクロン(µm2)またはミクロン(µm)よりも大きくする必要があります。これは、電子部品の電気的接点(electrical contact)のほぼ100倍、場合によっては1,000倍の大きさになります。しかも、光の散乱や透過損失を減らすためには、光学素子の側壁の粗さ(sidewall roughness)はナノメートルスケール(nm-scale)にする必要があります。電子部品の場合、ナノメートルレベルの側壁の平坦性を要求することは一般的ではありません。シリコンフォトニクス技術を実現するために、GlobalFoundriesの前身であるIBMなどのチップメーカーは、2000年代初頭(あるいはそれ以前)からシリコンフォトニクス技術の開発を進めており、2008年にはシリコンフォトニクス光接続の概念とプロトタイプを初めて正式に発表しました。Intelは、カリフォルニア大学サンタバーバラ校(UCSB)、スタンフォード大学(Stanford Univ)、マサチューセッツ工科大学(MIT)との長い共同研究の歴史があり、長年にわたってシリコンフォトニクス光連結技術を戦略的に展開し、深く根付かせてきました。単結晶薄膜エピタキシャル成長、構造設計、個々の光部品に必要な光学特性の最適化プロセスやフォトニックデザインオートメーション(photonic design automation, PDA)ソフトウェアの開発に加え、アクティブ光部品と光導波路の結合設計やプロセス統合をさらに進め、光集積回路やシステム(高密度波長分割多重光ファイバーバックボーン伝送システムなど)の実証も行っています。現在、Intelの最先端のシリコンフォトニクス技術は、チップ製造業界で主導的な地位にあると考えられます。シリコンフォトニックチップは現在、データセンターや5G通信などの技術分野に統合されており、大きなビジネスチャンスが生まれています。Google、Apple、Meta、Amazon、Microsoftなどの企業も、短距離データセンター内(850nmレーザーとマルチモード光ファイバー)および長距離データセンター間(1310nmレーザーとシングルモード光ファイバー)の光リンクを構築するための高効率シリコンフォトニック接続チップ技術の開発を積極的に進めています。Cisco、STM、IMEC、AIM Photonics、IMEなどの他の欧米の企業や研究機関も、シリコンフォトニック集積光回路とCMOS集積回路の統合に関する技術的手配をすでに行っており、オンチップ信号処理の速度と帯域幅のさらなる向上を目指しています。

シリコンフォトニクス技術は、回路基板間の光接続アプリケーション向けのファウンドリーサービスとしてウェハメーカーから提供されていますが、効率的で省エネルギーなコンピューティングのためにシリコンフォトニクスの真の利点を十分に活用するためには、オンチップ(on-chip)光接続を可能にする必要があります。しかし、チップファウンドリは現在、直接統合できる光源レーザー(lasers)を提供することができません。カリフォルニア大学サンタバーバラ校(UCSB)のJohn Bower教授は、2024年のIEDM国際会議での招待講演で、シリコンプラットフォーム上に直接統合された量子ドットレーザー光源を製造するために必要な主要技術と、大容量シリコンフォトニック集積回路を実現するための技術進化について詳細かつ洞察に満ちた説明を行いました[5]。一般的に、半導体薄膜レーザー光源は、レーザー放射を起こすために非常に大きな駆動電流を必要とします。しかし、長期間の動作中に動作温度が徐々に上昇すると、放出光の波長が赤方偏移(red shift)し、光強度も低下しやすくなります。そのため、温度安定性、信頼性、耐用年数が低いなどの課題があります。さらに悪いことに、シリコンは間接バンドギャップ(indirect bandgap)半導体であり、光から電気への変換効率は極めて低いです。幸いなことに、2008年にマサチューセッツ工科大学がゲルマニウム半導体レーザーの機能性を実証しました[6]。n型高濃度ドーピングと引張変形技術を用いることで、ゲルマニウム膜の間接バンドギャップを擬似直接バンドギャップ(pseudo-direct bandgap)に変換することができます。しかし、自由キャリア吸収(Free Carrier Absorption)効果によりレーザーの閾値電流密度(約280mA/cm2)が大幅に増加し、ゲルマニウムレーザーの動作寿命が短くなり、動作の温度信頼性と安定性にさらに課題が残ります。現在、III-V族レーザー光源とシリコンフォトニクスのアクティブ/パッシブ素子を統合する唯一の方法は、パッケージングまたはウェハボンディングです。しかし、パッケージングやウェハボンディングのコストは非常に高く、市場競争力の点で不利です。

一方、3次元量子閉じ込め効果により、量子ドットは光励起子(exciton)を内部に効果的に閉じ込めるため、レーザー放射を開始するために必要な駆動電流閾値は比較的小さく、高温環境でも安定して動作することができます。さらに、量子ドット内の分散したエネルギー準位は、量子ドットレーザーの単色波長の純粋化(スペクトル線幅は数十ナノメートル以下で、一般的なレーザー光源の線幅のわずか1/10)、パルスレーザーのモード同期の安定化、レーザーの長寿命化(1万倍)に役立ちます。[5] その上、量子ドットは調整可能な電子エネルギー構造を持つという量子物理的特性があり、配合によって量子ドットの直径を変えることで発光波長を調整することができます。量子構造レーザーの性能は、表面プラズモン共鳴(Surface plasmon resonance,SPR)などの工学的設計と組み合わせることで、さらに最適化できます。John Bower教授はまずシリコンプラットフォーム上の二酸化シリコン膜をエッチングしてシリコンを露出させ、InAs量子ドットを選択的にエピタキシャル成長させるという自身の研究室の研究を紹介し、高品質な量子ドットレーザー光源の具体的な成果を示しました。

量子ドットレーザーに加えて、窒化シリコン/シリコン光導波路と集積可能なゲルマニウム光検出器も、シリコンフォトニクスプラットフォームを実現するための重要な基盤技術の一つです。しかし、ゲルマニウム半導体のバンドギャップは約0.66eVと比較的小さいため、暗電流が高くなるという課題があり、光電変換の信号対雑音比と検出能力(detectivity)に影響し、エネルギー損失が深刻化する可能性があります。多くの研究では、量子ドットを光検出器の光吸収層に組み込むことで、暗電流が低減し、光キャリアの寿命、熱安定性、光応答が改善され、検出光の波長を調整したり、小型部品の厚さや面積を縮小したりできることが指摘されています[7]。そのため、量子ドット光源や光検出器に関する技術研究も盛んに行われています。

量子ドットレーザー光源やゲルマニウム光検出器などの部品の製造上の課題に加えて、シリコンフォトニクス技術の商用化に向けたもう一つの現実的な技術課題は、シリコンフォトニクスの能動部品と受動部品(半導体レーザー、光検出器、光変調器、光導波路、スプリッター、集光素子など)の設計を、正確で効率的に数値シミュレーションし、フォトニック集積回路システム全体の性能を評価する方法です。スタンフォード大学のJelena Vuckovic教授は、2024年のIEDM国際会議の招待講演で、自身の研究室が他の主要な研究機関、研究室、多くのウェハメーカーとの産学連携を通じて、高速で高性能な電磁(EM)シミュレーション解析ソフトウェアとハードウェア(Stanford Photonics Inverse Design Software, SPINS)を開発したことを発表しました。さらに、産学パートナーの成熟した製造プロセスを用いて、小型化された統合型フォトニック集積回路システムを試作、検証したことも示しました[8]。産業界と学界が緊密に連携した逆設計(inverse design)、のアプローチを通じて、同研究室とその協力機関はスケーラブルな量子および古典的シリコンフォトニクス集積光回路システム(Scalable Quantum and Classical Photonics)の実証に成功しました。たとえば、データセンター向けのブロードバンドマルチチャンネル光トランシーバーモジュールや、炭化ケイ素プラットフォーム上で自作の小型Ti:サファイアレーザーを用いてシリコンホール中の電子スピン量子ビットを制御する技術などがあります。

|

2. シリコンフォトニクスが量子コンピューティング技術に果たす重要な役割 |

Jelena Vuckovic教授が述べているように、シリコンフォトニクス技術は、従来の古典的コンピューティングの計算速度を向上させ、データセンターの伝送効率を高めるだけでなく、量子コンピューティングのための量子ビット技術の実用化を促進することが期待されています。実際、シリコン式であれイオントラップ(ion trap)式であれ、量子ビットの動作を真に実証するためには、量子状態を近距離で操作し読み出すシリコンフォトニクス集積回路が不可欠です。

室温で動作するとされているイオントラップ量子ビットの場合、現在の方法のほとんどは、光学テーブル上の光やマイクロ波信号を使用して、真空チャンバー内にあるイオントラップ量子ビットを遠隔操作しています[9]。イオントラップ量子ビットの量子状態は、光学テーブル上の高開口レンズを通して単一光子検出器に集光することで読み取られます。イオントラップ量子ビットの機能は室温、真空環境で検証されていますが、イオントラップ量子技術は、量子ビット数の拡大や量子状態の初期化/操作/検出の忠実度の向上という点で多くの技術的課題に直面しています[9]。

これは、光学部品と光ファイバーの複雑なアライメントや、機械的振動/熱ノイズなどの環境変動によって、イオントラップ量子ビットの読み取り忠実度を制限する多くの追加のノイズ源が発生するためです。真空環境下で光導波路を介してレーザー光源によりイオントラップ量子ビットを直接制御することができれば、同時に、単一光子検出器も光導波路に接続し、イオントラップ量子ビットの量子状態情報を直接読み取りCMOS 集積回路に出力し、後続の信号処理を行うことができるようになります。これにより、自由空間中の光学部品のジッタ/ドリフトや遍在する電気ノイズが排除されるだけでなく、極端に長い光ファイバーや光学部品間の複雑なアライメントの問題も解消されます。これは、イオントラップ量子ビットの読み取り忠実度を大幅に「向上」させるのに役立ちます。

|

2-1. 量子ビットへの応用におけるシリコンフォトニクスの技術的課題 |

シリコンフォトニクス素子技術の研究開発は30年以上の歴史がありますが、そのほとんどは、通信や従来のコンピューティングなどのアプリケーションを対象としています。これまでに開発されたシリコンフォトニクス関連技術(光導波路、光変調器、光検出器、さらには光源などの素子)は、通信アプリケーション向けの高速、高帯域幅、高応答、または高ワット数の光/電気信号の処理に重点を置いています。一方、シリコンフォトニクス素子をイオントラップ量子ビットの制御や読み取りに使用する場合は、低ノイズ、低暗電流、超低ワット数(光子数が少ない)の近紫外線や可視光信号を処理でき、低温環境でも安定して動作する必要があります。以下では、イオントラップ量子ビットアプリケーション向けシリコンフォトニクス素子の主要な技術要件と技術的課題について、要点を絞って説明します。

|

集積可能な窒化シリコン光導波路と回折格子 |

イオントラップ量子ビットを制御するために一般的に使用されるレーザー光源の波長域は、近紫外、可視、近赤外のスペクトルをカバーする約300-2000nmです。残念ながら、現在のシリコンフォトニクス技術で一般的に使用されているシリコン光導波路は、紫外線・可視光領域での吸収率が高く、光学特性の損失が大きいため、イオントラップ量子ビット技術には適していません。これに対して、窒化シリコン(Si3N4)光導波路はUV-可視波長範囲で透明で非吸収性であり、光学損失が低いことが特徴です[10,11]。窒化シリコンは、CMOS プロセス 技術で絶縁層、中間層、保護層として一般的に使用される材料であり、従来の化学気相成長(CVD)プロセスで堆積することが可能です。CVDプロセスは実際の用途に応じて微調整することができ、窒化シリコンの化学組成(SixNyやSiOxNy薄膜など)や屈折率を調整することで、窒化シリコン光導波路のモード数、光学限界、伝送損失を最適化することができます。窒化シリコン光導波路は、シリコン光導波路がカバーできない可視光帯域(400~1000nm)をカバーできるため、近年、特に量子通信/コンピューティングのためのさまざまな実験用チップの最適なプラットフォームとなっています[12]。

2020年にスイス連邦工科大学チューリッヒ[13]は、イオントラップチップと窒化シリコン光導波路を統合したイオントラップ量子論理ゲートを報告しました。実証されたイオントラップ量子論理ゲートは、シングルモード光ファイバーを用いて、729 nmの可視光を窒化シリコン光導波路に導入し、それを真空かつ低温環境にあるイオントラップチップに伝送するというものでした。この方法により、光学テーブル上の光学アライメントの問題や機械的振動、ビームスポットのドリフトを回避でき、量子論理ゲートの忠実度が改善されました。しかし、このときスイス連邦工科大学チューリッヒが実証したイオントラップチップは、光変調器や単一光子検出器などのシリコンフォトニクス能動素子とはまだ統合されていませんでした。これは、窒化シリコン薄膜上のゲルマニウムまたはシリコンゲルマニウムの核生成の滞留時間が非常に短く、選択的エピタキシャル成長法によって高品質の単結晶ゲルマニウムまたはシリコンゲルマニウム薄膜を成長させることが困難な為で、フォトニクス能動素子を続けて製造することが不可能でした。この問題を克服するため、(1)ウェハ接合を使用して窒化シリコンプラットフォーム上にSOIを接合し、ゲルマニウムやシリコンゲルマニウムの光学活性層をエピタキシャル成長させる方法[14]や、(2)STM、IHPおよびトロント大学のように、SOIプラットフォーム上にシリコンゲルマニウム変調器およびゲルマニウム光検出器を作製した後にPECVD法で窒化シリコン膜を堆積し、CMPで平坦化後に最上層の窒化シリコン光導波路を製作する方法[14-16]が提案されています。しかし、後者の方法では、最上層の窒化シリコン光導波路の製造後に、窒化シリコンの脱水素化や緻密化のための高温アニール処理を施すことが困難であり、窒化シリコン光導波路内部の欠陥数を低減することができません。これは、下部の光学活性領域(シリコンゲルマニウムおよびゲルマニウムエピタキシャル膜)の格子緩和を引き起こし、光学活性部品の性能低下につながるためです。これまでのところ、Ge/SiGe高速光変調器[14]、高速光検出器[14,15]、およびレーザー光源[17]を窒化シリコンプラットフォーム上にモノリシックに集積した報告はほとんどありません。したがって、光能動部品の製造と、窒化シリコンプラットフォーム上への光能動/受動部品の統合は重要な研究課題です。

|

チップ上に集積可能な単一光子検出器 |

量子ビットの量子状態信号は非常に弱く、周囲環境のノイズに干渉されやすいため、イオントラップ量子ビットの数個の光子数の変化を迅速かつ正確に読み取り、検出するために、直接「組み込む」ことができる単一光子検出器が必要です。単一光子検出器とイオントラップ量子チップを窒化シリコン光導波路で直接接続して、光子の「収集」と「検出」の間のクロストークを最小限に抑え、大規模なイオントラップ量子ビットアレイの測定の実現可能性をさらに拡大することができれば最適です。一般的に、イオントラップ量子ビットから放出される光子の波長は、主に300~500 nmです。しかし、現在利用可能な「最も成熟した技術」であるシリコンアバランシェ光検出器は、850nmの光しか検出できず、イオントラップ量子ビットの状態を直接検出することはできません。米国NISTの研究者らは、自作の内蔵型「超伝導」単一光子検出器を用いて、撮像レンズやカメラを必要とせずに、ベリリウムイオンの量子状態をほぼ完璧な精度(99.9%以上の精度)で読み取りました[18]。しかしながら、「超伝導」単一光子検出器は絶対零度に近い環境でしか正常に動作しないという制約があります。NISTが報告しているように、検出効率を効果的に高め、暗計数率を抑えるために、CMOS技術と互換性のある近紫外対応のシリコンベース単一光子検出器の開発が急務です。さらに、結合損失やノイズをさらに低減し、イオントラップ量子ビットの拡張性をより高めるためには、窒化シリコン光導波路/回折格子をシリコンベースの単一光子検出器とモノリシックに統合できることが必要です。

|

チップ上に集積可能な光源 |

イオントラップ量子チップと統合可能な単一光子検出器に加えて、窒化シリコン光導波路に結合された可視光光源は、イオントラップ量子チップを制御するための重要な要素です。John Bower教授がIEDMでの招待講演で述べたように、シリコン基板上に集積光源を実現することは、シリコンフォトニクス技術の最大のハードルであり、ましてや窒化シリコン光導波路と統合できる可視光源は言うまでもありません。

文献によれば、量子井戸、量子細線、さらには量子ドットなどのゲルマニウムナノ構造の使用により、シリコン基板上に単結晶ゲルマニウム膜を成長させる際の欠陥問題を効果的に緩和できることが報告されています。特に、量子閉じ込め効果によって、狭小なゲルマニウム量子ドット内では電子-正孔波動関数の強い重なり合いによりゲルマニウム量子ドットの光学遷移の振動強度が大幅に向上し、ゲルマニウムバルク材料が厳密に従わなければならないエネルギーと運動量(E-k)の保存則の制約を打破することができます。さらに、単一材料で作られたゲルマニウム量子ドットの直径を調整することで、発光のバンドギャップを調整して異なる波長の光を放出することができるため、従来のように、異なる波長の光源を生成するために異なるバルク材料を使用しなければならないという制限を克服できます。しかし、単一の量子ドットの発光体積は小さいため、共振器内に配置する必要があります。レーザー光が量子ドット/共振器に照射されると、パーセル効果(Purcell effect)により量子ドット内で光励起された光子の数が急増し、全体的な発光品質係数が向上します。一般的に使用される量子ドット共振器構造には、フォトニック結晶、マイクロディスク、マイクロリングなどがあります。フォトニック結晶アレイの構造設計の複雑さ(テンプレートの厚さ、穴の直径、周期、欠陥モードなど)と製造精度に対する極めて高い要件(サブミクロンレベルの穴(直径または周期)を露光するための高度なリソグラフィーシステムの使用)を考慮すると、ミクロンレベルのマイクロディスクまたはマイクロリングと共振器の設計と製造は比較的容易であり、さらに、放出された面内(in-plane)光を隣接するバス導波路と結合することができ、オンチップでの集積にも適しています。

マイクロディスク共振器は、主に円盤状の光学的に高密度な媒体内に光場を閉じ込め、マイクロリング共振器の端部でディスクの径方向で共振を起こし、ウィスパリングギャラリーモード(whispering gallery mode, WGM)を発生します。マイクロディスク共振器は、電極や導波路の設計と製造において大きな柔軟性とコスト上の利点を備えています。近年、欧米の研究機関は、シリコン、ゲルマニウム、二酸化ケイ素、窒化シリコンなどのマイクロディスク共振器にさまざまな(シリコン、ゲルマニウム、CdSeなどの)量子ドットを組み込み、光励起マイクロレーザーを実証したと報告しています。フランスのCNRS-Univ.は、一連の論文を発表しました[19]。この論文では、まずガリウムヒ素基板上に300nm厚のn+-ゲルマニウムをエピタキシャル成長し、次にフォトリソグラフィーとエッチングによりゲルマニウムのマイクロディスクを製造し、さらに、窒化シリコンを堆積してゲルマニウムマイクロディスクを覆い、引張歪を導入したn+-Ge活性発光層を形成し、光励起型のゲルマニウムマイクロレーザーを実証しました。しかし、Ge-on-GaAsプロセスをシリコンプラットフォームに移行するのは困難です。東京都市大学は、隣接する導波路と電気的に結合してエレクトロルミネッセンスを発生できるPINゲルマニウム量子ドットマイクロディスクダイオードを提案しました[20]。しかし、ほとんどの量子ドットマイクロディスクはSOIプラットフォーム上で作られており、可視光源には適していません。イオントラップ量子チップとスムーズに統合できる量子ドット/窒化シリコンマイクロディスク可視光源の開発が急務となっています。

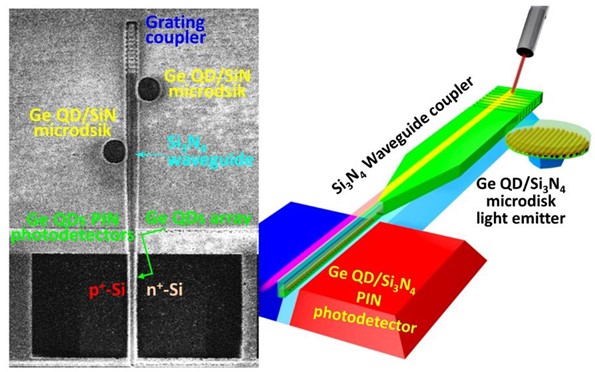

本実験チームは、2022年のIEDM国際会議[21]において、窒化シリコン導波路(格子結合器と導波路コーンを含む)、ゲルマニウム量子ドットマイクロディスク光源、および光子検出器をモノリシックに集積し、図1に示すように、近紫外可視光イオントラップセンシングアプリケーションに使用できることを報告しました。

図1. 窒化シリコンに埋め込まれたGe量子ドット光検出器と発光素子 |

|

我々は、完全なCMOSプロセス技術を使用して、直径と空間位置を制御可能なゲルマニウム量子ドットアレイを製造しました。単一ステップの選択的酸化で、窒化シリコン膜上のリソグラフィーで定義された多結晶シリコンゲルマニウム柱を、窒化シリコンに埋め込まれたゲルマニウム球状量子ドットへと変換することが可能です。我々のゲルマニウム量子ドットの最も重要な特徴は、900℃の熱酸化によって製造されるため、図2に示すように、高い熱安定性を持つという利点があることです。この固有の熱安定性の利点により、上部または下部の窒化シリコン導波路にエバネッセント結合できるGe QD光検出器と発光素子の可能性が開かれます。デバイスの製造と統合の観点では、上部導波路との結合構造は、デバイス(光検出器と発光素子)の設計と3次元統合の材料の選択に柔軟性を提供します。上部導波路結合構造により、「導波路」と「基板」を同じ材料で構成する必要がなくなります。我々の自己組織化による窒化シリコン内埋め込みゲルマニウム量子ドットアレイ構造法は、窒化シリコンマイクロディスク発光素子とPIN光検出器を上部または下部の窒化シリコン導波路に統合する柔軟性と、3次元PIC統合の実現可能性を提供します[22]。我々が開発したゲルマニウム量子ドット製造技術は、CMOSプロセス技術を直接利用しており、優れたプロセス制御と部品設計における工学的優位性を持ち、量子ビット、単電子トランジスタ、光トランジスタなどを直接製造することが可能で、実用化と産業化の可能性を備えています。これは、量子コンピューティングや光接続などの技術の発展に寄与するものです。 |

図2 TEM、HAADF STEM、およびGe(緑)、N(赤)、O(白)のEDSマップにより明らかに示された、SOI基板上のSi3N4中に形成されたSiO2/Ge QDの自己組織化ヘテロ構造の形成 P. W. Li et al., IEDM Tech. Dig. pp. 451-454 (2022) より引用 |

Reference:

[1] Y. J. Mii, “Semiconductor industry outlook and new technology frontiers,” IEDM Tech. Digest, 1.1, Dec. 2024

[2] S. K. Yeh et al., “Silicon photonics platform for next generation data communication technologies,” IEDM Tech. Digest, 23.3, Dec. 2024

[3] C. H. Fann et al., “Novel parallel digital optical computing system (DOC) for generative AI,” IEDM Tech. Digest, 31.7, Dec. 2024

[4] H. Hsia et al., “EPIC-BOE: An electronic-photonic chiplet integration technology with IC processes for broadband optical engine applications,” IEDM Tech. Digest, 31.8, Dec. 2024

[5] J. Bower, “Integrated quantum dot lasers and high capacity silicon photonic integrated circuits,” IEDM Tech. Digest, 23.1, Dec. 2024

[6] RE Camacho-Aguilera et al., “An electrically pumped germanium laser,” Optics Express, vol. 20, no. 10, pp. 11316-11320, 2012

[7] Hongmei Liu, Fangfang Zhang, Jianqi Zhang, Guojing He, “Performance analysis of quantum dots infrared photodetector,” Proceedings of SPIE, vol. 8193, 81930J (2011)

[8] Jelena Vuckovic, “Scalable quantum and classical photonics,” IEDM Digest, 26.3, Dec. 2024

[9] K. Brown et al., “Materials challenges for trapped-ion quantum computers,” Nat. Rev. Mater. vol. 6, pp. 892–905 (2021).

[10] D. J. Blumenthal et al., “Silicon nitride in silicon photonics,” Proc. IEEE, vol.106, 12 (2018).

[11] P. Munoz et al., “Silicon nitride photonic integration platforms for visible, near-infrared and mid-infrared applications,” Sensors, vol.17, 2088(2017).

[12] A. Orieux et al., “Recent advances on integrated quantum communications,” J. Opt., vol. 18, 083002 (2016).

[13] K. Mehta et al., “Integrated optical multi-ion quantum logic,” Nature vol. 586, pp. 533–537 (2020).

[14] F. Boeuf et al., “A silicon photonics technology for 400 Gbit/s applications,” IEDM Tech. Digest, pp. 775 (2019)

[15] S. Lischke et al., “Silicon nitride waveguide coupled 67GHZ Ge photodiode for non-SOI PIC and EPIC platforms,” IEDM Tech. Digest, pp. 779 (2019)

[16] W. Sacner et al., “Monolithically integrated multilayer silicon nitride-on-Si waveguide platforms,” Proc. IEEE, vol. 16, 2232 (2018)

[17] S. Bao et al., “Low-threshold optically pumped lasing in highly strained germanium nanowires,” Nat Comm. vol. 8, 1845 (2017)

[18] S. L. Todaro et al., “State readout of a trapped ion qubit using a trap-integrated superconducting photon detector” Phys. Rev. Lett. 126, 010501 (2021)

[19] A. Ghrib et al., “Tensile-strained germanium microdisks,” Appl. Phys. vol. 102, 221112 (2013)

[20] X. Xu, T. Maruizumi, and Yasuhiro Shiraki, “Waveguide-integrated microdisk light-emitting diode and photodetector based on Ge quantum dots,” Optics Exp., vol. 22, 3905 (2014)

[21] C. H. Lin, P. Y. Hong, B. J. Lee, H. C. Lin, T. George, and P. W. Li, “Monolithic integration of top Si3N4-waveguided germanium quantum-Dots microdisk light emitters and PIN photodetectors for on-chip ultrafine sensing,” IEDM Tech. Dig. pp. 451454, Dec. 2022.

[22] C. H. Lin, P. Y. Hong, B. J. Lee, H. C. Lin, T. George, and P. W. Li, “Self-organized germanium quantum-dots/Si3N4 enabling monolithic integration of top Si3N4 waveguided microdisk light emitters and PIN photodetectors for on-chip sensing,” IEEE Trans. Electron Dev. vol. 70, no. 4, pp. 2113-2120 (2023)