摩尔定律预测,集成电路上的晶体管数目,在相同面积下,每隔 18 个月数量就会增加一倍,芯片效能也会持续提升,此定律在引领半导体产业发展近 60 年之后,也逐渐走向极限,各大厂也相继思索找寻新解方,希望可以在无法缩小晶体管的情况下,持续提升芯片整体效能,并透过系统整合方式,来层层堆栈半导体电路,达到性能的跃进,而其技术关键就在于「封装」的「异质整合」方案来延续摩尔定律,而先进封装其最大优势,就是大幅缩短了不同裸晶间的金属连导线距离,因此传输速度大为提升,也减少了传输过程中的功率耗损。

目前各家晶圆厂与封测厂皆发展自家先进封装技术,从技术及资本支出来看,以英特尔与台积电投入最为积极,两家合计投入的资本支出达整体产业 55%,技术也最为领先。

|

|

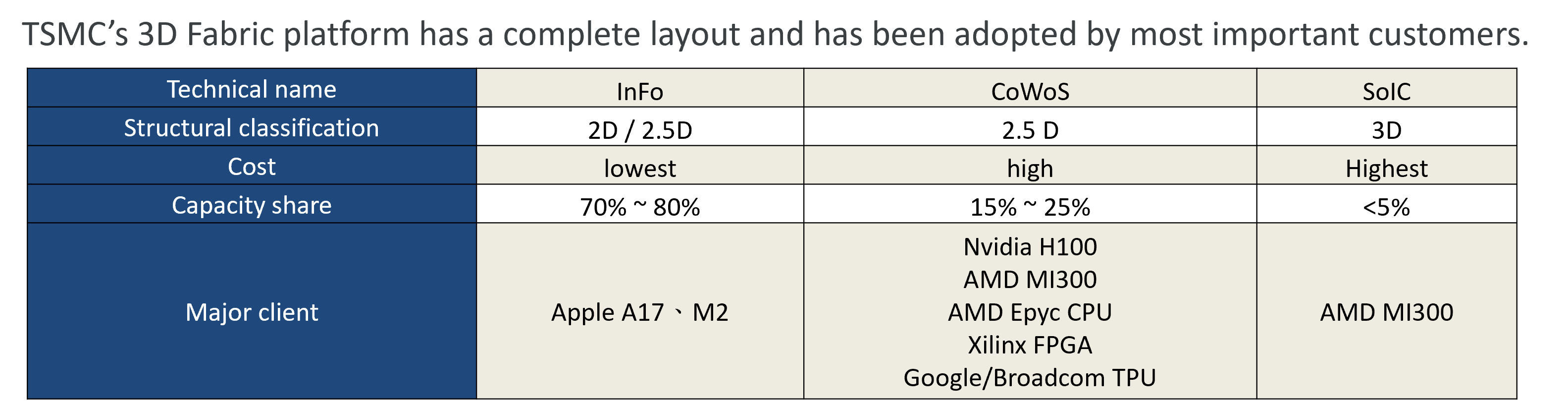

以台积电来说,其先进封装技术可分为 2D 的 InFO(扇出型封装)、2.5D 的 CoWoS(Chip on Wafer on Substrate)以及 3D 的 SoIC。其中 InFO 技术最成熟也最便宜,约占其先进封装产能的 70~80%(每年 8~10 万片),并已大量使用在 Apple 的 A 系列及 M 系列芯片。近年AI芯片需求趋势庞大,也进一步催动了先进封装CoWoS的产能需求,连带让半导体行业向来较不被重视的「测试」产业,也因先进封装热潮有了新样貌。闳康也持续保持着与产业趋势共进的策略,针对先进封装的失效分析已具备非常丰富的分析经验,以下就针对其关键性的应用工具及技术一一解密。

|

|

|

2D X-ray |

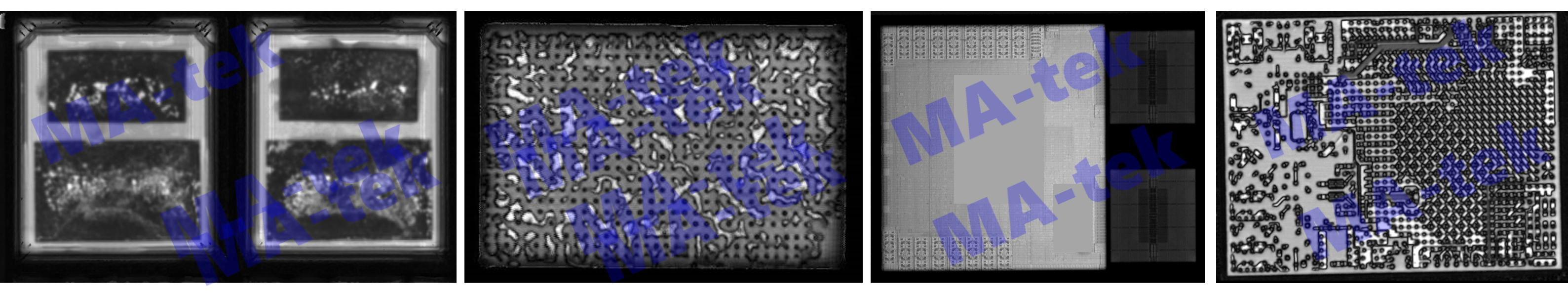

藉由高能量撞击金属靶材激发出的x-ray具有穿透特性,借此成像以观察及判断先进封装内部是否存在空焊、HIP或Hop 等现象,也可透过此工具快速的确认封装内是否有断线与严重烧融等缺陷。

|

|

|

SAT |

SAT又称为CSAM,藉由超音波于不同密度材料的反射速率及回传能量的不同而形成影像,并依超音波的穿透率选用不同频率的探头藉以侦测先进封装内部各接口层是否有脱层、空洞或是裂缝等异常现象。

|

图三 SAT在封装健检中扮演查找封装内部缺陷的角色 |

|

3D x-ray |

什么状况下需要使用3D X-RAY机台呢? 当失效样品仅有一个,无法直接进行破坏性分析时,我们建议可以针对异常区域执行超高解析的非破坏性3D X-RAY机台。闳康目前拥有ZEISS Xradia 520与620 Versa高分辨率三维X光显微镜( High Resolution 3D X-ray Microscope)设备。其原理就是以高能电子重击金属靶材(W)后,产生短波长、高能量且具有强穿透性的 X-ray 射线,穿透待测物产生绕射波,侦测器接收后,经由闪烁体转换成可见影像,并利用样品在载台上360゚旋转的方式得到空间中各种不同方位的 2D X-ray 断层影像,并配合计算机演算将这些影像组合成待测物的 3D X-ray 断层影像,这也是计算机断层成像的原理。3D X-ray的分辨率取决于pixel size(像素大小),当pixel size越小,分辨率越好。目前机台在空间分辨率的极限为0.5um,且机台内有12种标准Filter(滤镜)可以自动调整,侦测器有5种镜头(0.4X、4X、20X及40X)可使用。

|

图四 3D X-ray的硬件架构 |

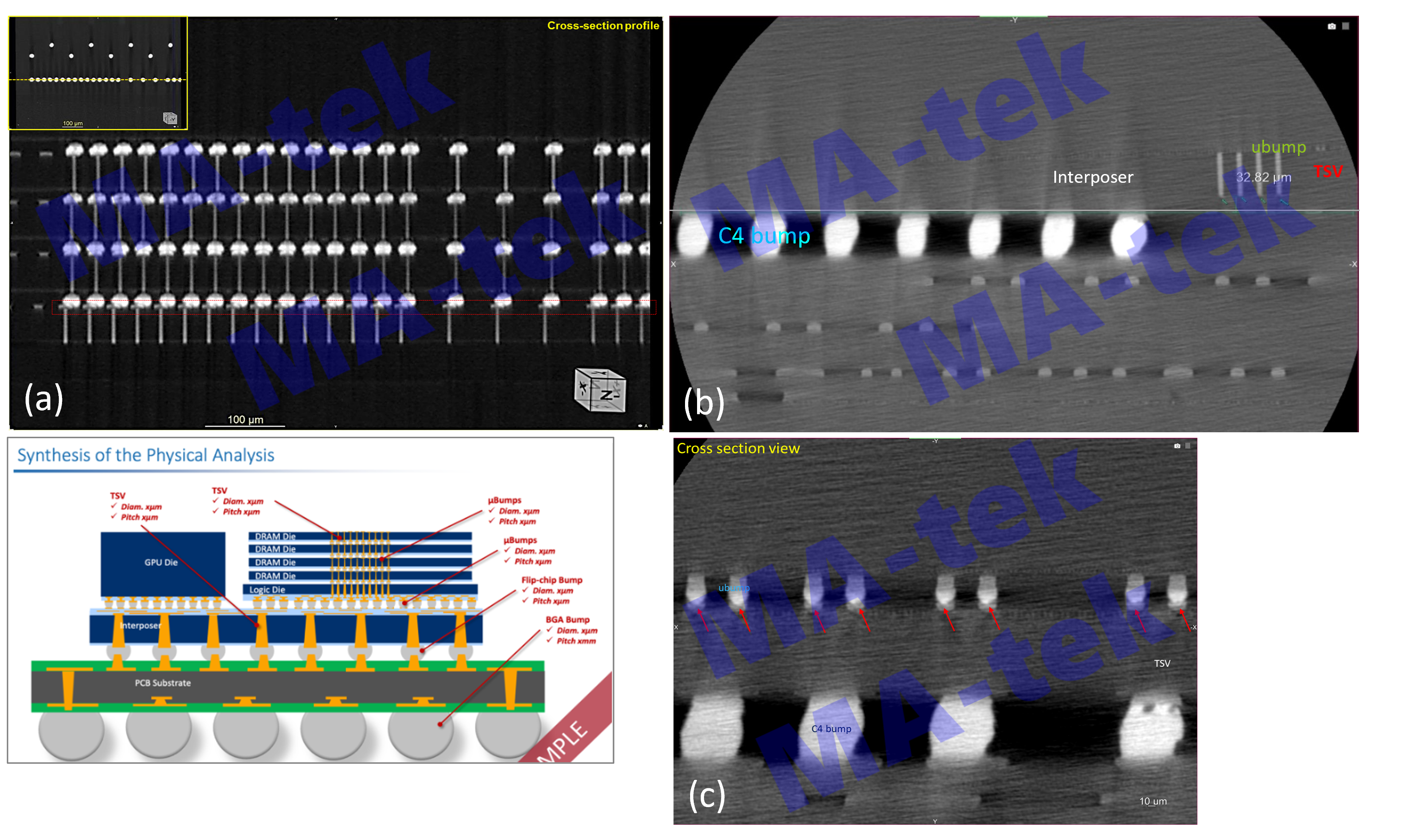

先进封装结构相对复杂,失效的样品若可以透过电性分析缩小异常范围,3D X-Ray即可以在较佳的扫描分辨率找出明显的缺陷,以下主要是针对CoWoS样品扫描之范例,图五(a)可以明显看出TSV异常位移,图五(b) 介质层(Interposer)有脱层现象,图五(c) u-bump接合处有明显异常。

|

图五 CoWoS封装结构示意图[3]与常见的缺陷类型 |

|

TDR |

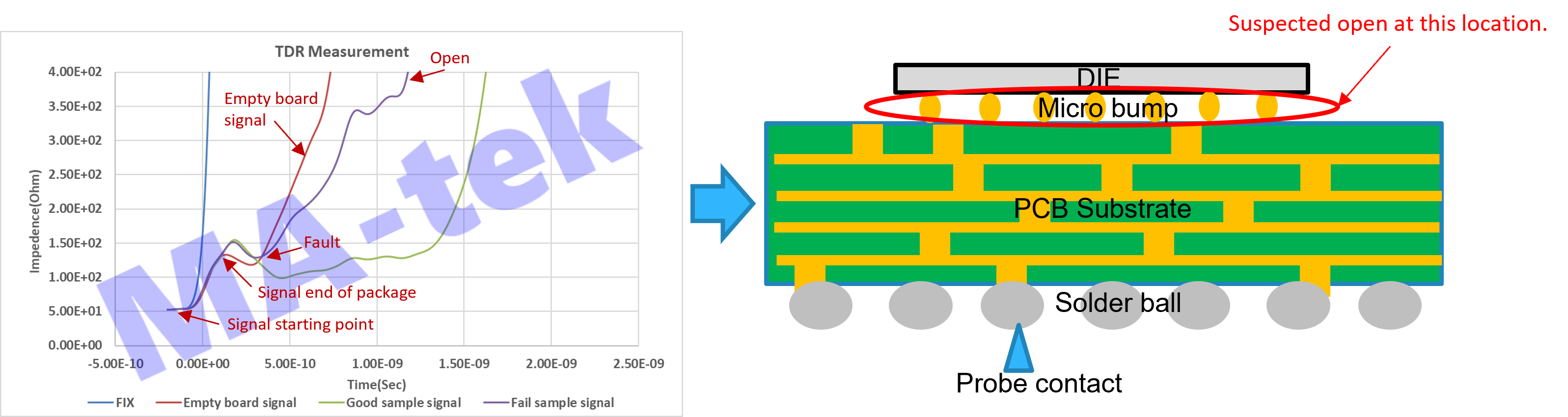

时域反射仪(Time Domain Reflectometry,TDR)是一种常用的网络分析技术,主要用于测量信号在传输线或传输介质中的反射和衰减情况。在先进工艺中,TDR 技术在失效分析方面具有重要作用,尤其在先进封装失效排除方面可快速、便利的区分异常是发生于芯片还是封装端,主要应用在半导体制造和测试过程,以及在电子设备的维修和失效排除中。

TDR 技术能够快速、准确地检测到断路,其原理是利用发射的短脉冲信号沿着被测试的线路传输,如封装或芯片内部的连接线路,然后测量信号反射的时间和强度。当传输线路是完整的时候,TDR 测量所得的反射信号将显示出一个典型的波形,但如果传输线路中出现了断路,则反射信号将会出现异常,例如反射信号的强度突然变弱或消失,或者反射信号的时间延迟不符合预期,在透过好品、坏品、空板的分析结果,可以准确地确定断路的位置,是封装中的芯片还是封装本身的断路,甚至可以推断封装中是哪个结构有异常,比如先进封装中最常见的u-bump, TSV或C4 bump结构或界面的问题。

|

图六 比较好品、坏品与空板的TDR的波形,判断可能的断点是在u-bump |

|

Lock-in Thermography(LIT) |

LIT又称为thermal emission microscopy,可非常有效及快速的对2.5D与3D 的先进封装失效热点进行定位,此外,有缺陷的半导体装置通常会表现出局部功耗的变化,导致局部温度升高,LIT能够通过红外热成像技术来检测物体表面的温度分布,从而识别出可能存在的故障或问题,并利用锁定(lock-in)红外线热成像来提高定位的精准度,以提供后续非破坏性(3D X-ray)与破坏性切片的封装缺陷观察结果。

LIT是利用高灵敏度之InSb(锑化铟) 侦测器侦测待测物在通电状态下,缺陷位置所产生的热辐射,藉以定位失效所在位置,甚至可估算出热源纵深相对距离,其特点与应用概述如下:

- 高分辨率红外热成像:配备了高分辨率的红外热成像技术,能够捕获物体表面微小温度变化的细节。

- 故障检测和分析:透过检测物体表面的异常温度,可以快速识别出潜在的问题,例如电子组件的过热或设备的热失效等等。

- 可检测的故障机制:应用于产品短路、ESD 缺陷、氧化物破损、装置闩锁、有缺陷的晶体管与二极管。

总的来说,thermal emission microscopy是一种功能强大的热影像分析仪器,能够帮助快速准确的进行故障分析定位。

|

图七 thermal emission microscopy可以在不开盖的情况下侦测失效点在平面上的位置,也可以在纵向上判断失效点存在于哪一层芯片或基板上 |

|

Plasma FIB (P-FIB) |

在封装与芯片的失效分析上,最初以研磨切片为主要分析方案,随着封装种类进步与多元,芯片内的I/O密度也快速地提高[4],其中提升芯片互连的接点密度,是2.5D/3D 立体封装的发展趋势[5],当接点间隙缩小至 10 微米以下时,手工研磨将不足以准确的制备定点样品切片,而P-FIB 在先进封装的失效分析上逐渐成为主要运用手法之一。

|

图八 各种封装技术在 1x1cm^2 的芯片内能达到的接点数量[4] |

P-FIB 的应用除了结构的基本观察以外,更可使用在热点或非破坏分析之后的检测验证上,比如以 Thermal Emission Microscopy、OM、3D X-ray 或 SAT 观察到异常之后,便可利用 P-FIB 在异常处做截面上的确认。[6]

|

图九 针对(a) 3D X-ray 观察到TSV变形位置执行 (b) P-FIB粗挖 + FIB 细修 |

DB P-FIB切割面积可达500um宽与500um深,可用于观察先进封装的结构,比如 C4 bump/interposer/u-bump/TSV/fine pitch RDL,在削切截面的过程中,同时以 SEM 方式观察削切的情形,可实时判断缺陷的变化。

|

图十 FIB 切削TSV 的连续过程 |

|

样品制备P-Lapping |

样品制备(sample preparation)在失效分析中扮演着至关重要的角色,是决定分析成功率的最大因素,尤其在先进封装失效分析流程中更加关键。透过制备的过程,包括手工/自动研磨、化学蚀刻等步骤,每一个细节都考验着操作人员的经验和细心程度。闳康团队在高阶先进封装领域拥有丰富的经验,藉助成熟的样品制备能力,我们成功地发现了封装内部各种缺陷。

图十一 P-Lapping手工研磨技术 (BGA) |

图十二 P-Lapping手工研磨技术 (InFO_oS) [7] |

|

SEM样品制备前处理 |

样品制备前处理及搭配电子显微镜观察是对先进封装失效分析常使用到的方式,其处理的手段会直接影响到最终的观察及分析结果,以下列举几个SEM样品制备的重要性质。

- 去除污染和杂质: SEM能够以极高的分辨率观察样品表面,因此在进行观察之前,样品必须经过适当的清洁,以去除任何可能影响结果的杂质或是可能污染机台的液体、挥发物以及粉尘。

- 提高导电性: SEM样品要求良好的导电性,以避免在分析过程中静电放电,这可能损害样品并对拍摄影像产生干扰,因此部分非导电物质在进行SEM拍摄之前皆会进行表面镀金或镀碳,以提高影像质量。

- 适当的固定和切割: 因SEM载台大小有限,样品需要裁切以利能够被固定在载台上,目前闳康所使用的机型可以放置六吋晶圆以内大小的样品,高度限制为1.5公分,目前常使用的材料都能够进行裁切,例如晶圆、载板、陶瓷材料、金属、玻璃、高分子材料等。

- 获取特定区域的信息: 如果有特定的垂直结构需要观察,这时候就需要做定点样品制备(切片),透过研磨以及抛光,甚至是离子束切片,我们可以精准的切到约1um大小的结构并进行SEM拍摄,更小的目标也可以藉由FIB和TEM来进行样品制备与拍摄。

- 提高分辨率和对比度: 正确的样品制备可以帮助提高SEM的分辨率和对比度,我们藉由一些表面处理来获得更多样品讯息,常使用的方式为化学药品的表面微蚀、离子束的表面抛光或深切、Plasma清洁等等。

透过上述介绍的相关手法,我们在研磨之前还必须先将样品以环氧树脂镶埋,目的是为了保护样品的结构,避免在研磨过程中对样品层次造成损坏,同时也要注意使用的砂纸号数以及材料,避免砂纸颗粒过大对样品造成不必要的损伤,最后再以抛光液以及绒布进行最后的加工,如此可以得到一个光滑平整的截面,以利SEM的拍摄及异常观察。

|

图十三 BGA封装经过研磨后再以SEM针对异常处放大观察 |

搭着AI的浪潮,高运算芯片与先进封装的产值在半导体产业愈趋成长,其设计与结构上的复杂度使得故障分析面临空前的挑战,而在先进封装的失效解析中,只要秉持本篇文章所述的各个环节与精髓,在缺陷的定位与观察上一定有莫大的帮助。

Reference:

[1] Yole

[2] Fugle

[3] EETimes

[4] King-Ning Tu, Chih Chen, Hung-Ming Chen, Electronic Packaging Science and Engineering, Wiley, 2021

[5]https://www.matek.com/zh-TW/Tech_Article/detail/specialist-column/all/202207-IAR (3D IC封装:超高密度铜-铜异质接合)

[6] https://www.matek.com/zh-TW/services/index/P-FIB

[7] https://3dfabric.tsmc.com/chinese/dedicatedFoundry/technology/InFO.htm